efinity-update

Efinity2023.1がリリースされました

はじめに

「Efinity統合開発ソフトウェア」は、Efinix社が提供するFPGA開発ツールになります。

ユーザー登録後にライセンス申請をすると無償で利用可能です。

v2023.1がリリースされたので、こちらの新しい内容についていくつか見ていきたいと思います。

v2023.1のリリース内容

- デバイス関連

- T20Q100F3、T13Q100F3(フラッシュ内臓)のサポート追加

- SPIフラッシュブロックのサポート(T20Q100、Ti60F100)

- Ti90/Ti120/Ti180のタイミングモデル(ファイナル)

- Spread-Spectrum(SSC) PLL のサポート

- SLVS I/O スタンダードのサポート

- その他

- Netlist Viewer (新機能)

- Block RAM Initial Content Updater (新機能)

- SDC 制約サポートの改善

- Code Editorの改善

- 論理合成

- sync_keep (pragma) をサポート

- carry skip (option) をサポート

- 配置配線

- 有効スキューのサポート

- IPコアサポート

- AXI Data FIFO Core の追加

- BRAM Wrapper Core の追加

- IPリリースノート v2023.1.150

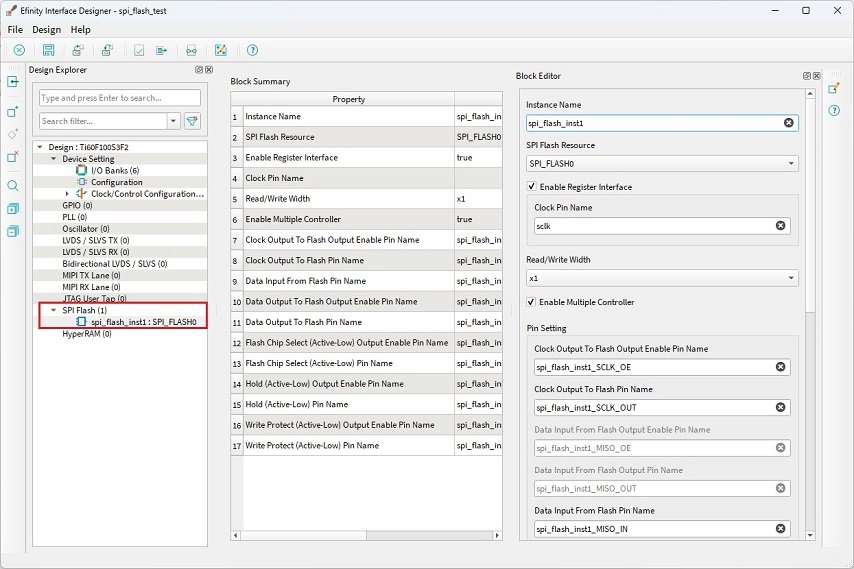

SPIフラッシュブロックのサポート

Efinix社のFPGAラインナップにはSPIフラッシュを内臓したものがあります。

最近追加されたFPGAについて、Efinityが対応しました。

内臓フラッシュは "Interface Designer" のSPIフラッシュのブロックで設定を行います。

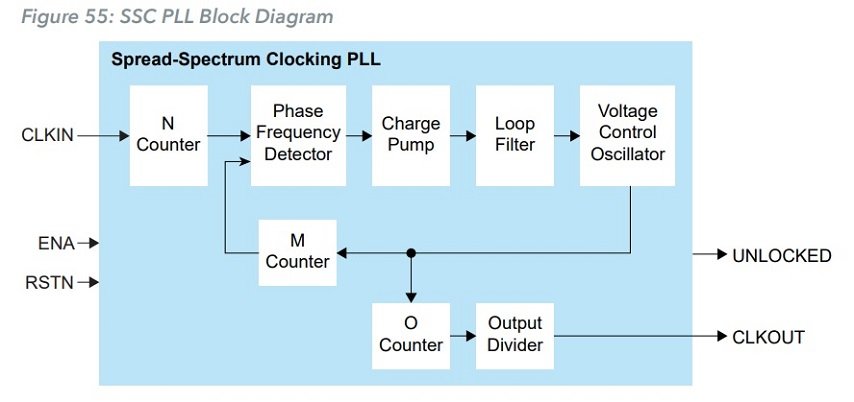

Spread-Spectrum(SSC)PLL のサポート

スペクトラム拡散クロッキング(SSC)はクロックによって生じるスペクトルのピークを下げ幅を広げます。

これにより、EMI(放射ノイズ)の発生量を少なくできます。

Ti90/Ti120/Ti180 のMIPI D-PHYインターフェスには、スペクトラム拡散クロッキング(SSC)PLL が搭載されています。

デフォルトでは通常のPLLとして動作します。SSCの機能を使うには、"Enable Spread Spectrum Clock (SSC)"オプションを有効にする必要があります。

Interface Designer でPLL SSCブロックがあるので、個々に追加します。

※ "ENA"を1に切替で動的にイネーブルできます

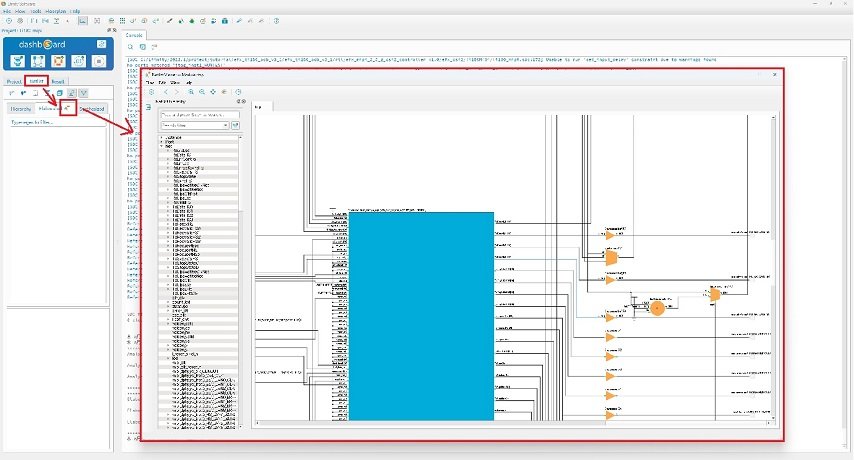

Netlist Viewer

ネットリストの回路をグラフィカルに表示するRTLビューワになります。ただし、ベータ版となります。Netlistタブに切り替えて Elaborated の横にあるアイコンをクリックで表示できます。net, port, instanstance を指定して検索もできます。

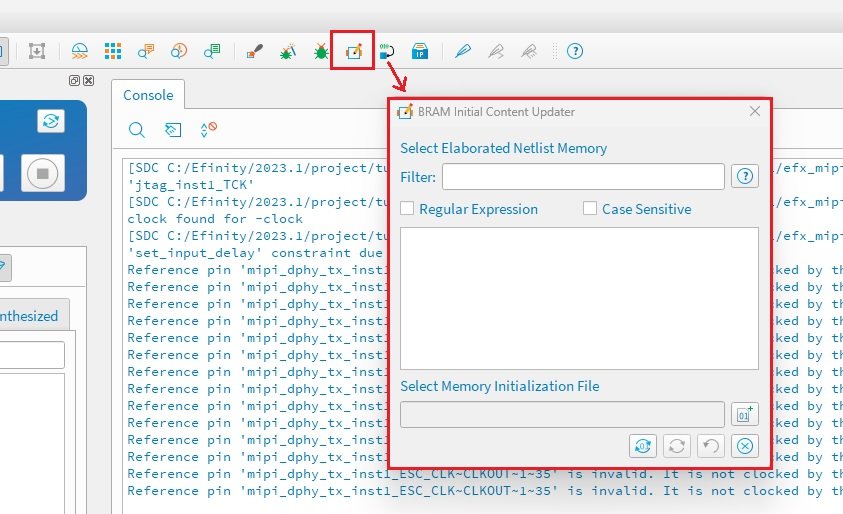

Block RAM Initial Content Updater

"BRAM Initial Content Updater" はコンパイルし直すことなく、FPGAのBRAMに保存された初期メモリを素早く更新するツールになります。

ネットリストメモリを選択してアップデートを行い、新しい .memファイルに置き換えます。

例えば、次のような場合に利用できます。

- オンチップメモリ内のRISC-Vアプリのコードを更新

- FPGA BRAM内に格納されたパラメータ

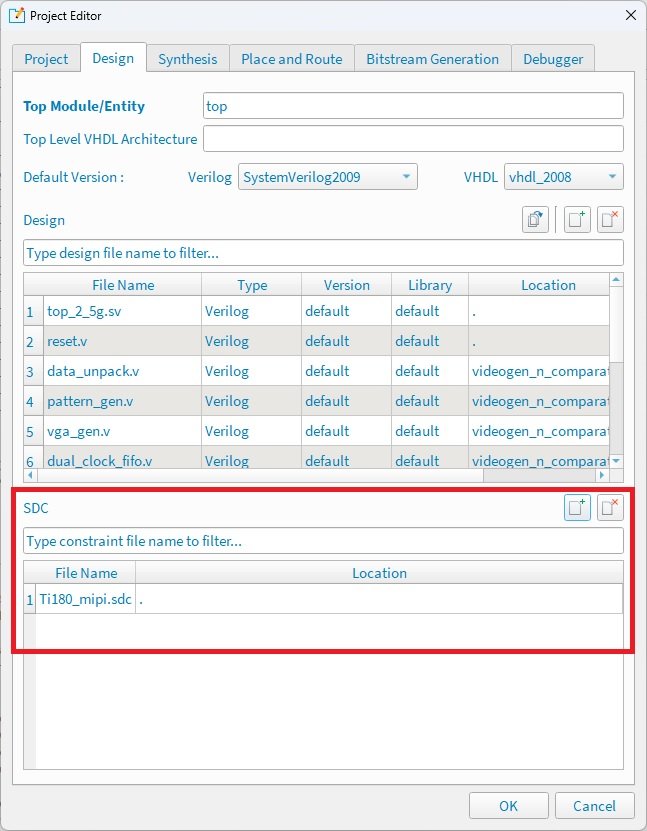

SDC 制約サポートの改善

複数のSDCファイルをサポートするようになりました。

"Project Editor > Design"で複数のSDCファイルを選択できます。

また、set_input_delayとset_output_delayで-add_delayのオプションが使えるようになりました。

set_input_delay -clock intclk 0.4 [get_ports d1]

set_input_delay -clock intclk 0.45 [get_ports d1] -clock_fall -add_delay -reference_pin intclkout

set_output_delay -clock intclk 0.3 [get_ports q]

set_output_delay -clcok intclk 0.35 [get_ports q] -clock_fall -add_delay -reference_pin intclkout

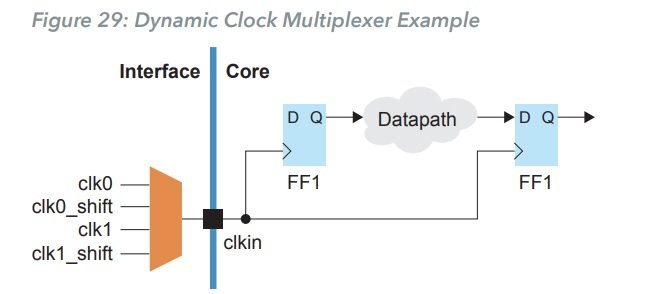

さらに、同じターゲットで複数のクロックを定義するcreate_clockの-addオプションが使えるようになりました。

create_clock -period 10 [get_ports clkin] -name clk0

# The following constraints use -add to avoid overwriting the previous setting

create_clock -period 10 –waveform {2.5 7.25} [get_ports clkin] -name clk0_shift -add

create_clock -period 20 [get_ports clkin] -name clk1 -add

create_clock -period 20 –waveform {4 16} [get_ports clkin] -name clk1_shift -add

# The four clocks are exclusive because they cannot operate at the same time

set_clock_groups -exclusive -group {clk0} -group {clk0_shift} -group {clk1} -group {clk1_shift}

syn_keep (pragma) をサポート

signalまたはwireに適用でき、最適化によってsignalを最小化または削除しません。

Velilog HDL

(* syn_keep = "true" *) wire x;

VHDL

attribute syn_keep: boolean;

attribute syn_keep of x : signal is true;

carry skip (option) をサポート

こちらはTitaniumのみのサポートになります。

Synthesisのオプションでinsert-carry-skipがサポートされました。

デフォルトはリップルキャリー加算器で、加算器のキャリー(桁上げ出力)をカスケード接続するため、段数が増えるとその分遅延が大きくなります。

しかしこのオプションを使うことで、面積を犠牲にしてスピード優先にすることができます(キャリースキップ加算器)。

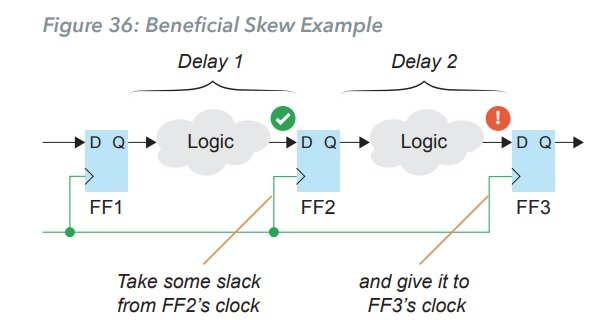

有効スキューのサポート

こちらはTitaniumのみのサポートとなります。

配置配線のオプションでbenefical_skewがサポートされました。

"Benefical Clock Skew"は配置配線を最適化するためのオプションで、ソフトでクロックを調整して、タイミングをより近づけます。

図のように、Delay1でタイミングを満たしていて、 Delay2でタイミングを満たしていないものがあるとします。

Delay1からいくらかスラックをとり、Delay2に与えることで両方のタイミングを満たすように調整します。

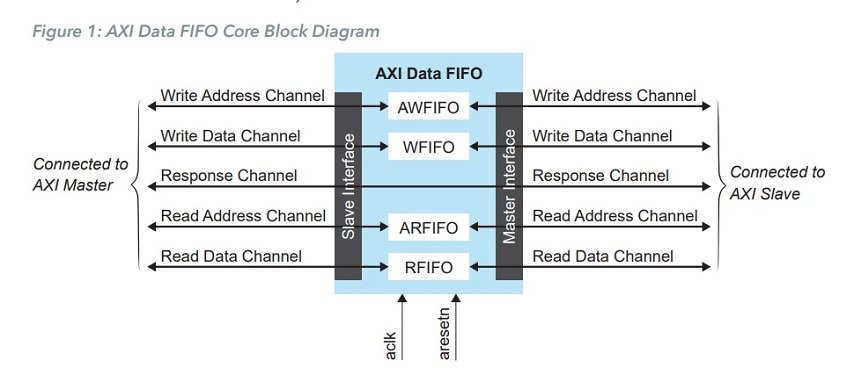

AXI Data FIFO Core の追加

"AXI Data FIFO Core"は、リードチャネルとライトチャネルの両方にFIFOバッファを提供します。

リードおよびライトチャネルの、アドレスとデータのFIFOは有効または無効にすることができます。

IPマネージャを使用してIPを選択、カスタマイズを行えます。

詳細は AXI DATA FIFO Core | Efinix をご確認ください。

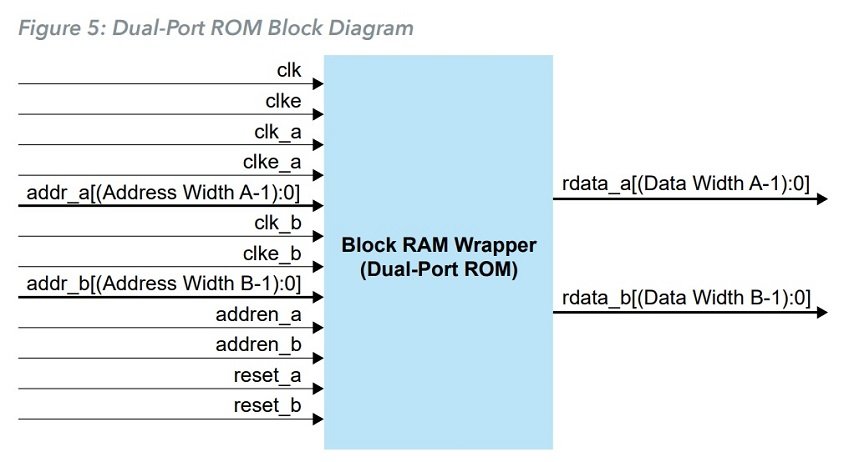

BRAM Wrapper Core の追加

"Block RAM Wrapper Core" はFPGA内の組み込みブロックメモリを使用し、メモリプリミティブの利用を最適化します。

BRAMラッパーはポートAとポートBで構成され、共有メモリ空間内でのread/writeのインタフェースとして機能します。

詳細は Block RAM Wrapper Core | Efinix をご確認ください。

- Single-port RAM (SP RAM)

- Simple Dual-port RAM (SDP RAM)

- True Dual-port RAM (TDP RAM)

- Single-port ROM (SP ROM)

- Dual-port ROM (DP ROM)

お問い合わせ

FPGAを使った開発やEfinixへの置き換えに興味がありましたらこちらまでお問い合わせください。

開発についてのご相談なども受け付けています。

https://www.explorer-inc.co.jp/contact/efinixcontact.html

ご質問・ご相談などは

こちらから

お問い合わせください。