efinity-update

Efinity2024.1がリリースされました

はじめに

「Efinity統合開発ソフトウェア」は、Efinix社が提供するFPGA開発ツールで無償利用できます。

v2024.1の新機能について見ていきたいと思います。

v2024.1のリリース内容

- サポートするFPGAの追加

- Titanium FPGAでトランシーバをサポート

- デザインファイルをパッケージ化する"IP Packager"を追加

- Titaniumのコンパイル時間を短縮

- タイミング解析用のTclスクリプトを改善

- トランシーバブロックのPython APIをアップデート

- IPのアップデート

サポートするFPGAの追加

Titanium FPGA は新たにN1156(1156ピン)のパッケージが増え、User I/Oは337ピンまで増えました。Efinity 2024.1で新たに対応するFPGAを表にまとめます。

ビットストリームにチェックが入っていないものは、ビットストリームファイルが生成されません。

最新の対応状況については Efinity 2024.1リリースノートをご確認ください。

| FPGA | パッケージ | ビットストリーム | 備考 |

|---|---|---|---|

| Ti375 | N1156 | ✓ | 新規追加 |

| Ti240 | N1156 | 新規追加 | |

| Ti165 | N1156 | 新規追加 | |

| Ti375 | N484 | 新規追加 | |

| Ti240 | N484 | 新規追加 | |

| Ti165 | N484 | 新規追加 | |

| Ti135 | N676 | 新規追加(パッチ適用が必要) | |

| Ti85 | N676 | 新規追加(パッチ適用が必要) | |

| Ti60 | F256 | ✓ | ビットストリーム生成をサポート |

| Ti35 | F256 | ✓ | ビットストリーム生成をサポート |

Titanium FPGAでトランシーバをサポート

TrionやこれまでのTitanium FPGAで扱う高速信号はMIPI(2.5Gpbs)でしたが、

今回サポートされるFPGAから PCI Express や 10GBASE-KR が利用できます。

トランシーバをサポートするFPGAは以下になります。

- Ti375N1156/N484

- Ti240N1156/N484

- Ti165N1156/N484

- Ti145N676

- Ti85N676

トランシーバは、PCIe Gen4、10GBase-KR、SGMIIの複数のプロトコルをサポートし、

PMAダイレクトモードもサポートしています。

また、トランシーバ確認のため、Ti375 PCIe Early Access Boardも提供されています。

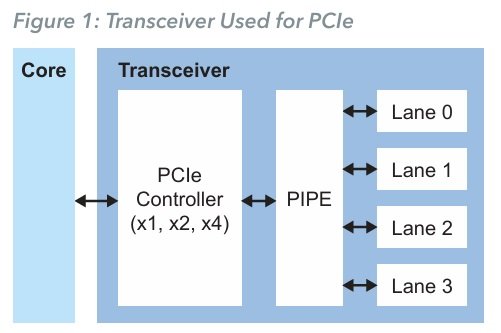

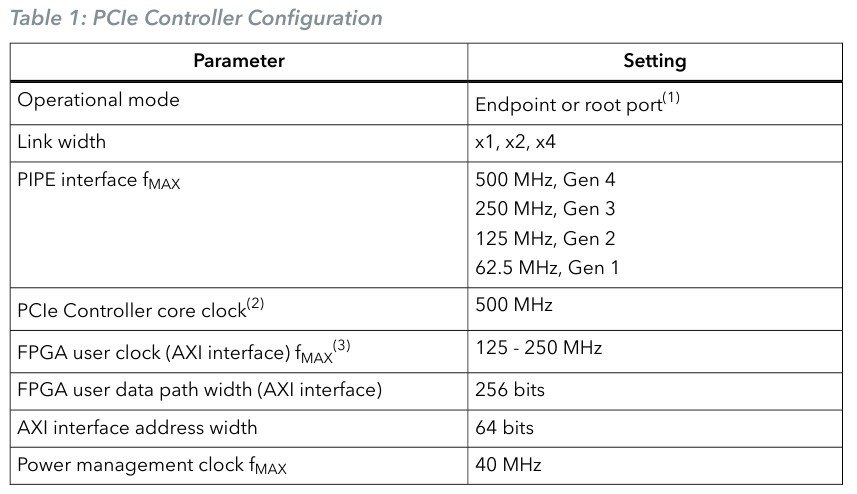

PCI Express

PCIe Gen1~Gen4 の x1/x2/x4 をサポートしています。

Gen4ならデータレートはレーン当たり最大16Gbpsとなります。

さらに、Root Port または Endpoint に設定できます。

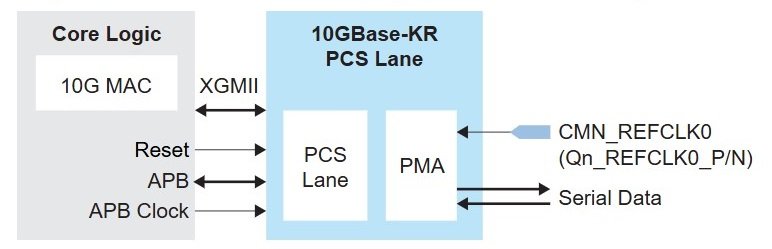

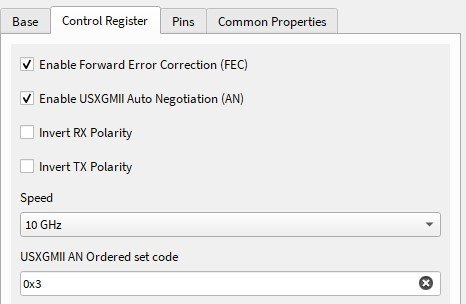

10GBase-KR

10GBase-KRのインタフェースは、最大10.3125Gbpsのデータレートをサポートします。

FEC(Forward Error Correction)やオートネゴシエーションのON/OFFを設定できます。

トランシーバのバンクは"quad"と呼ばれ、各quadは4つのレーンを持ち、各レーンで10GBase-KRインタフェースをサポートしています。

トランシーバの数はパッケージにより異なります。

使用するFPGAで利用可能なトランシーバの数はデータシートをご参照ください。

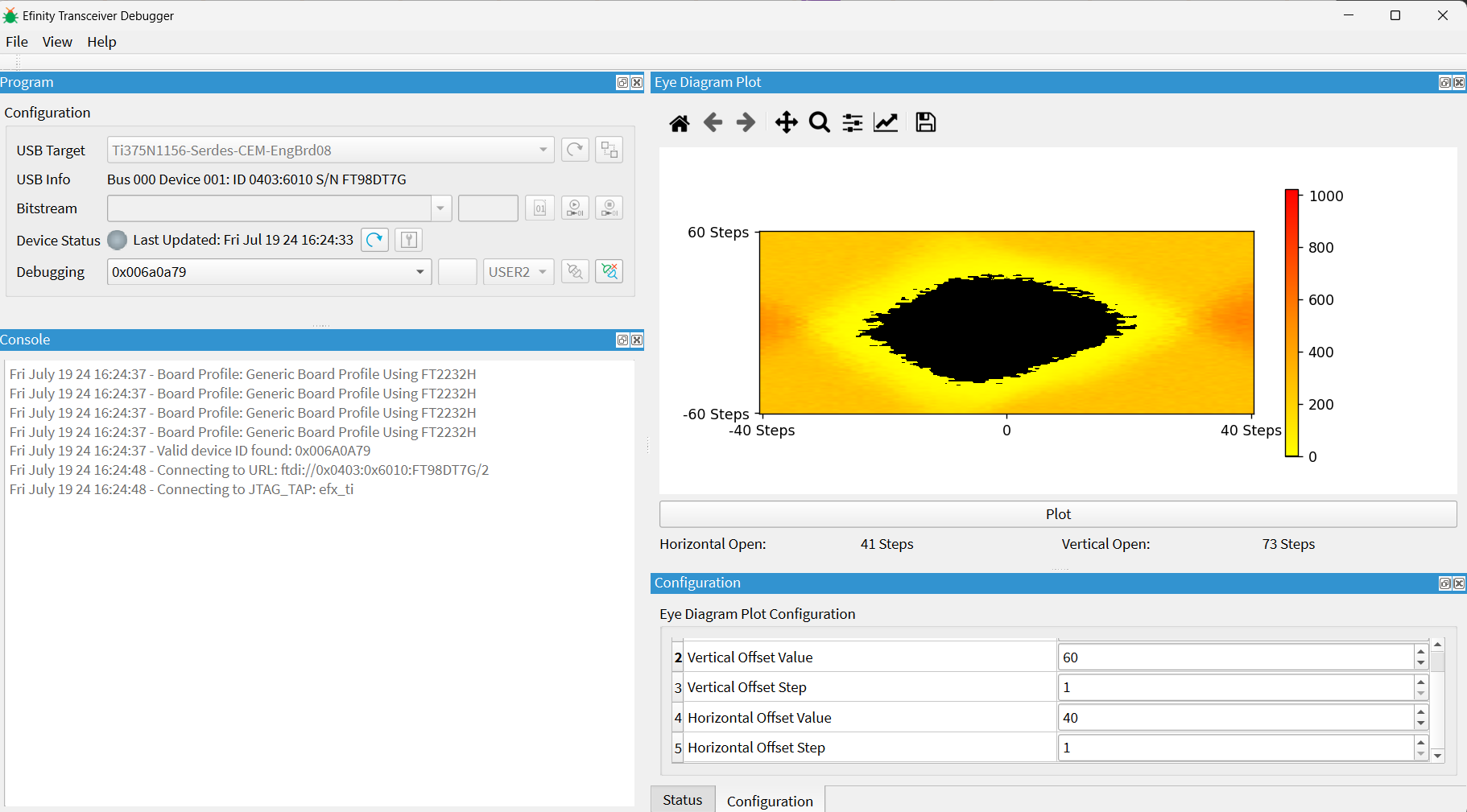

トランシーバ用のデバッグツールを追加

Efinity v2024.1からトランシーバデバッガーが追加されました。

このツールはコマンドからの起動になります。

Windowsの場合

<Efinityインストールフォルダ>\debugger\serdes_debug_tool\bin\efinity_serdes_dbg.batトランシーバデバッガーを使うことで、トランシーバの信号品質をテストおよびアイパターンの表示ができます。ただし、ベータ版で提供のため機能が制限されていますのでご注意下さい。

- 1quadのみサポート

- アイパターンの channel 0 のみアクセス可能

- JTAG Programmer や Efinity Debugger などの他のJTAGツールと同時使用をサポート

- ハードウェアが異なるUSERタップに制限(トランシーバデバッガーのデフォルトはUSER2)

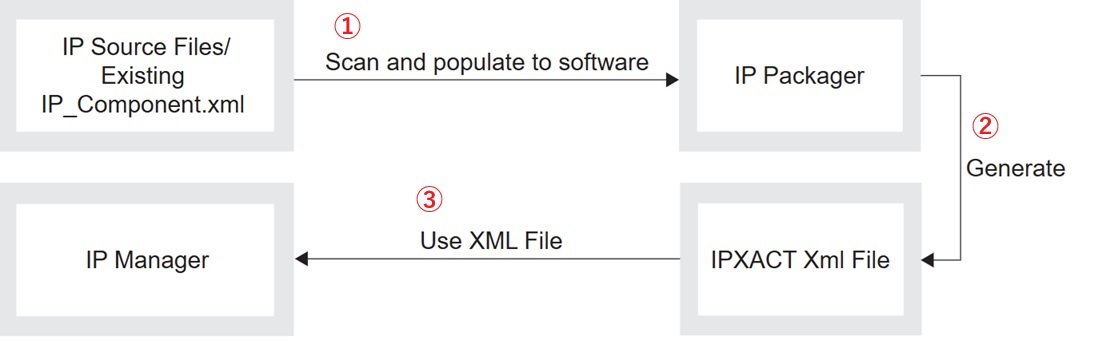

デザインファイルをパッケージ化する"IP Packager"を追加

"IP Packager"は、デザインファイルをスタンドアロンとしてパッケージ化できるツールになります。

自作IPコアを IP Manager でカスタマイズできるようになります。

この機能は、同じコードを複数のプロジェクトで利用する場合に役立ちます。

ここでは簡単に使い方について説明します。

今回は、全加算器をN個使ったNビット加算器のモジュールをIP化してみます。

詳しくは Efinity IP Packager User Guide をご確認ください。

- Efinityプロジェクトを開きパッケージ化したいソースを追加、Synthesisを実行

- パッケージ化する前にRTLデザインのコンパイルできることを確認しておくこと

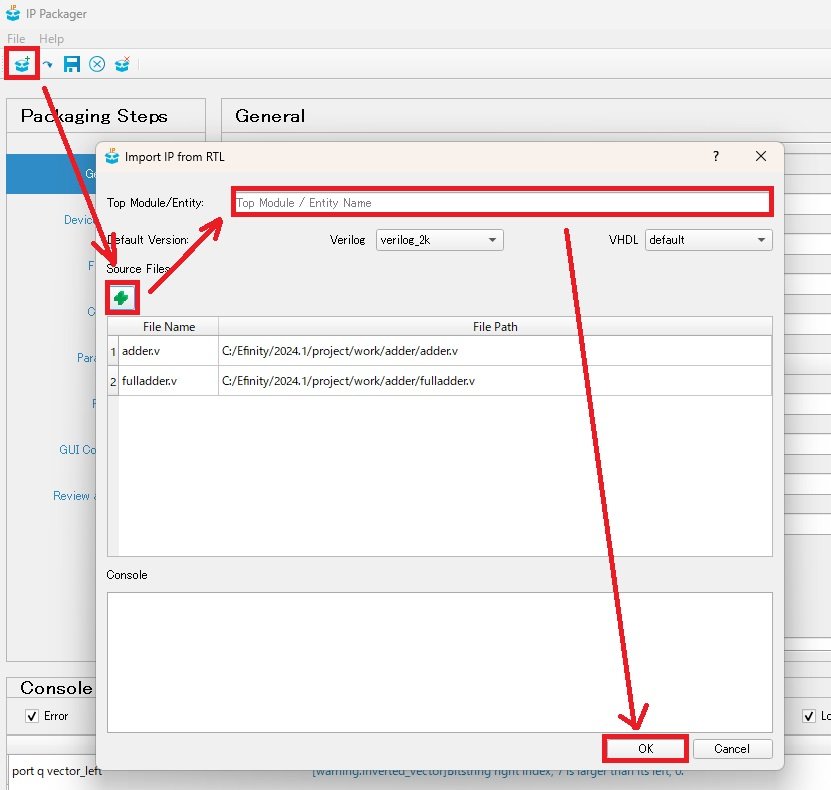

- "Open IP Package"アイコンをクリックし、IP Package を開く

- ① パッケージ化するRTLデザインのインポート

- "Import IP"のアイコンをクリックし、"Import IP from RTP" のウィンドウを開く

- +ボタンを押し、該当のデザインをインポート

- トップモジュールの名前を入力

- OKをクリックすると、RTLの解析が実施

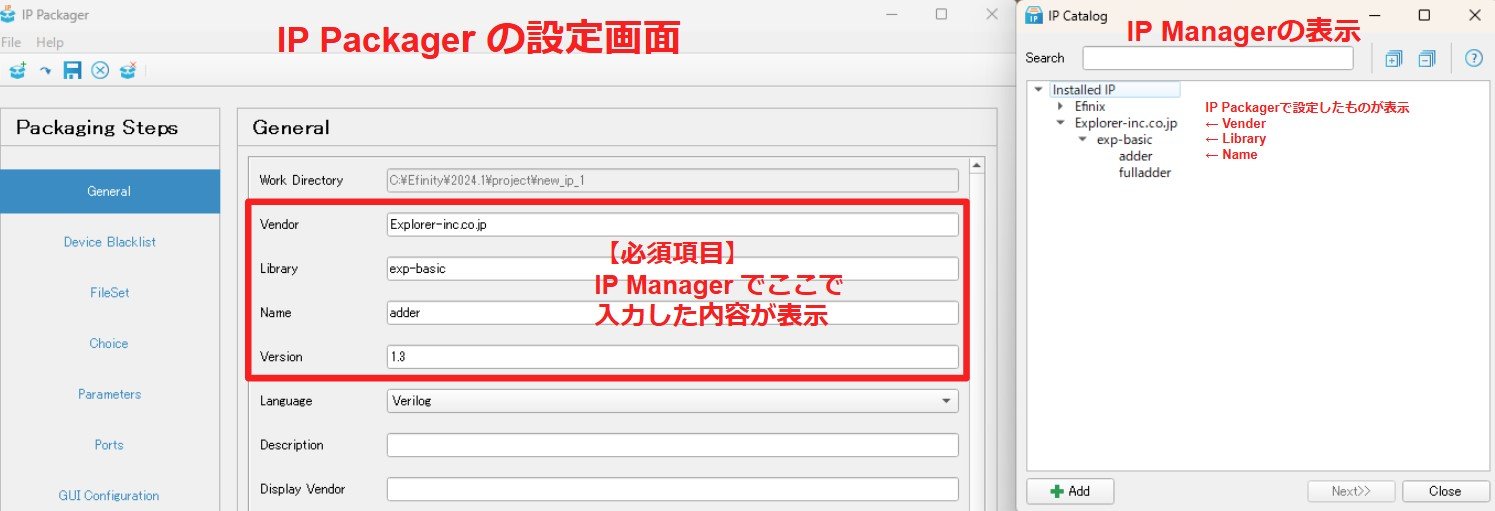

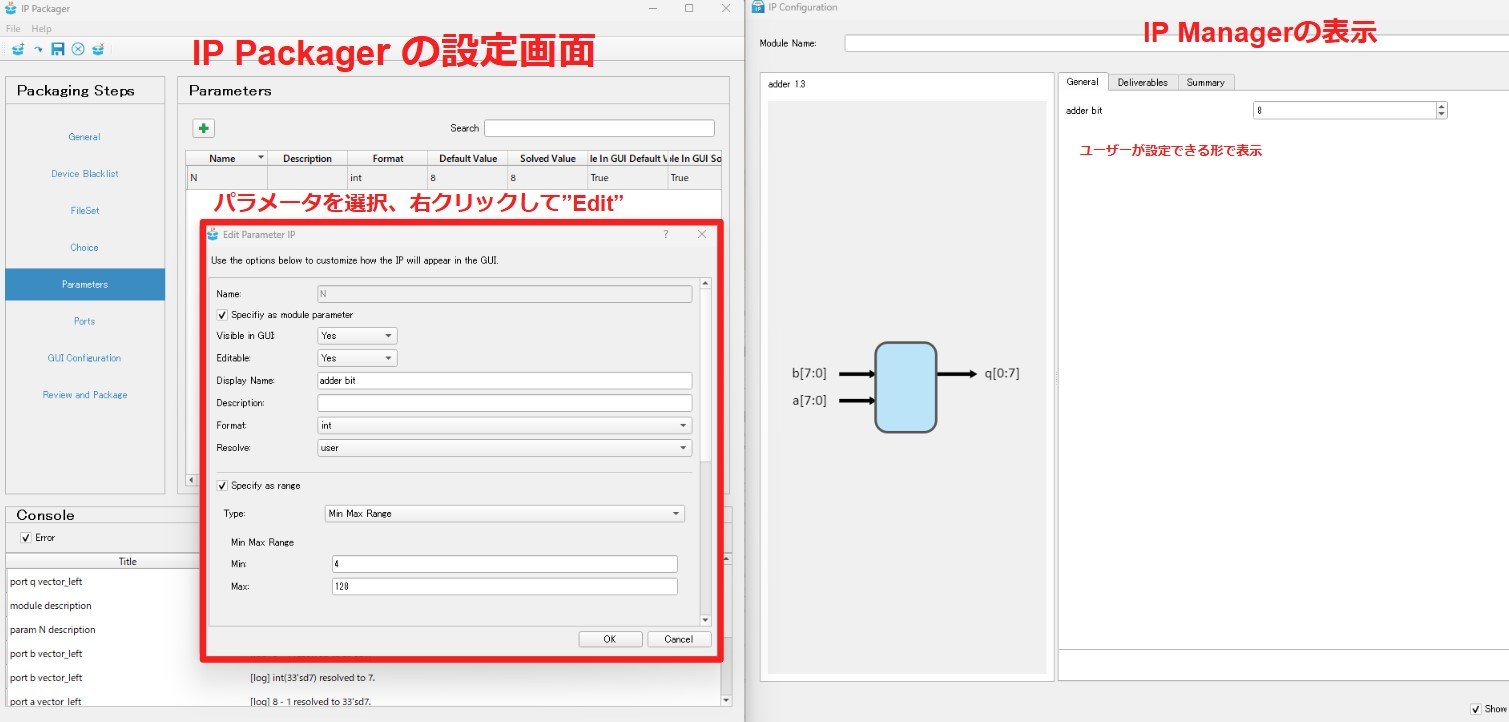

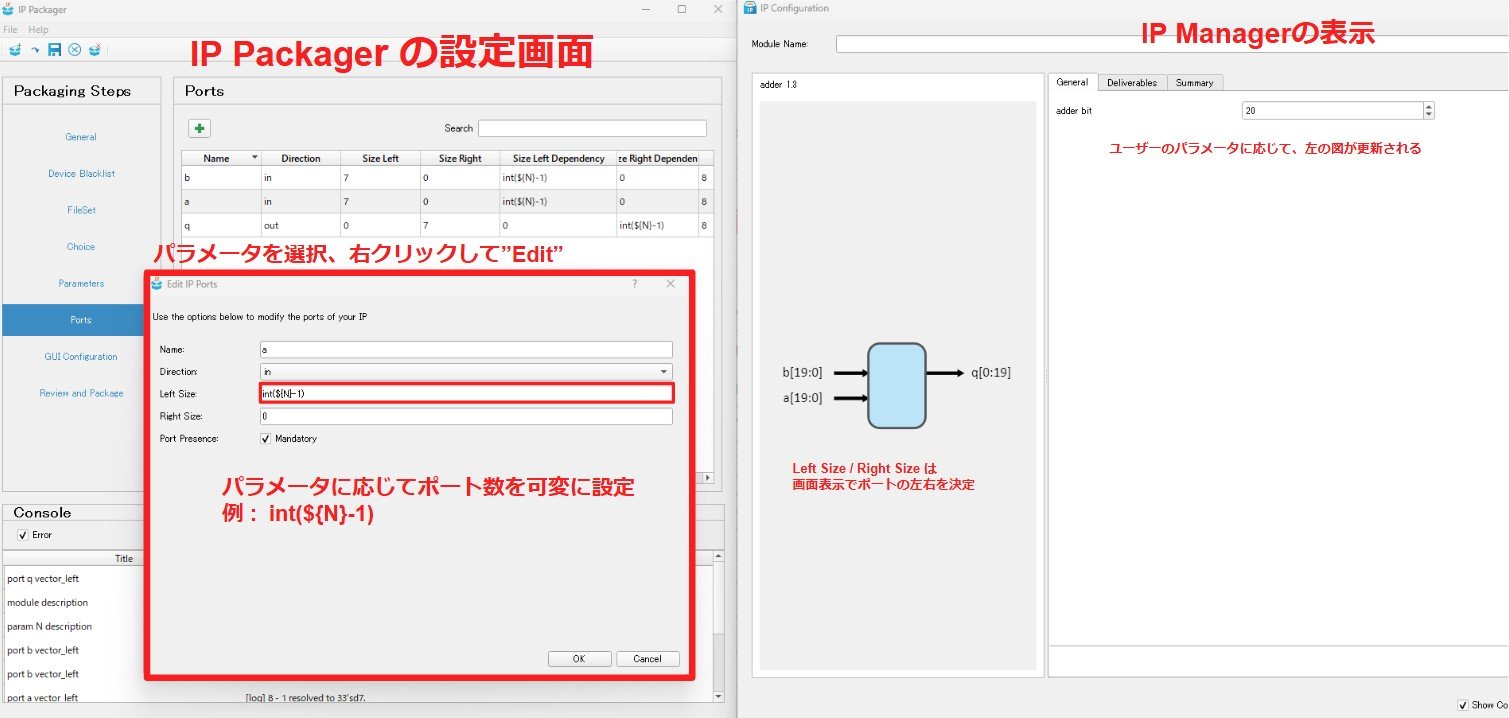

- ② IP Manager用の設定を行う

- "General" : IP Managerを開いた際の表示を設定

- "Device Blacklist" : IPがサポートしないFPGAのパッケージを指定

- デフォルトはすべてのデバイスに対応

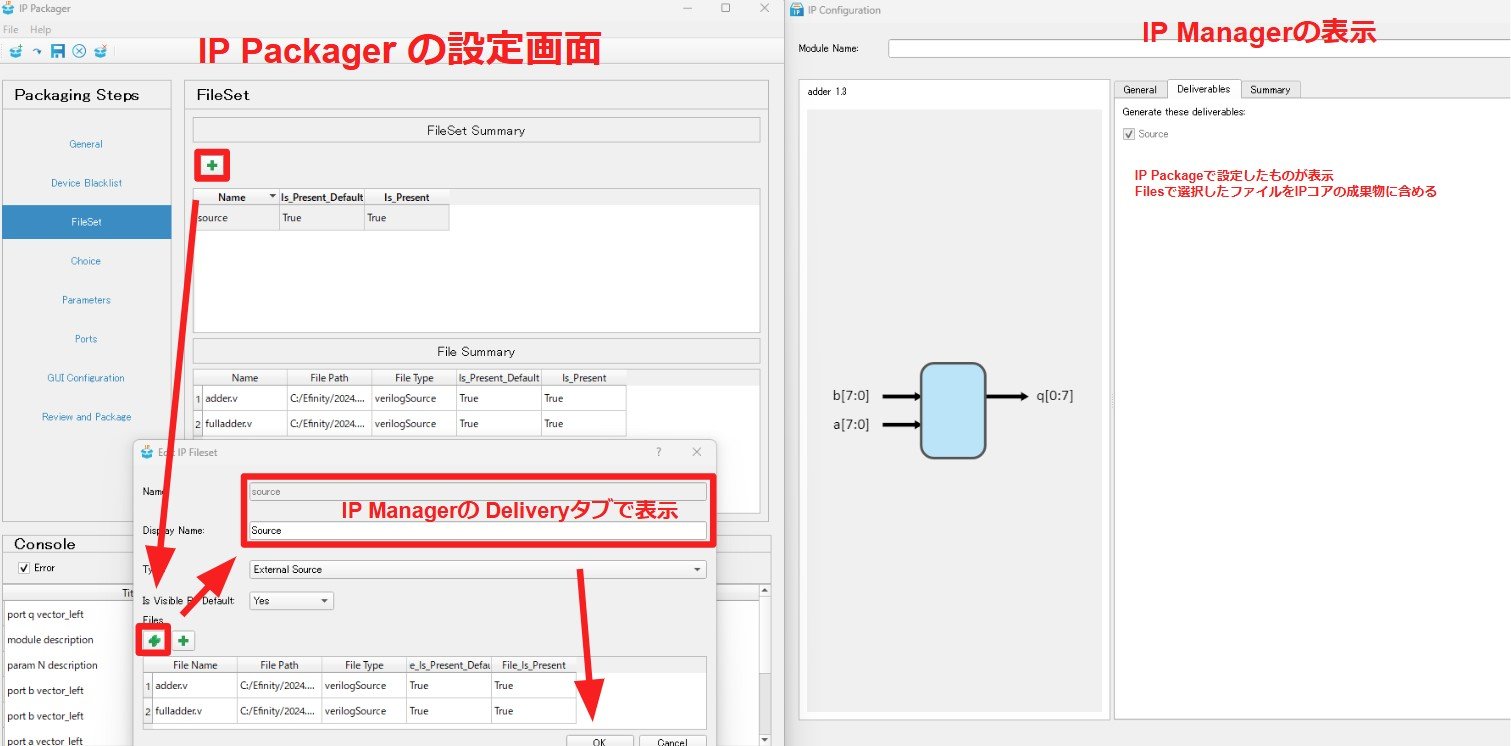

- "FileSet" : IPに関係するファイルを整理、IP Mangerの"Delivery"タブで表示

- "Choice" : 事前に定義した選択肢を持つパラメータを作成

- テキストの場合は""のダブルクォーテーションで囲むこと

- "Paramters" : IP ManagerのGUIでカスタマイズできるユーザー設定可能なパラメータを追加

- ①でスキャンされたパラメータが表示されるので、項目を右クリックしてEdit

- "Port" : モジュールの入出力ポート信号を設定

- ①でスキャンされたポートが表示されるので、項目を右クリックしてEdit

- "GUI Configuration" : IP Managerで表示するタブ表示のカスタマイズ

- "Review and Package" : IPをパッケージする設定の確認、パッケージの生成

- "Package IP" でデザインファイルと設定のチェック

- "Package IP and Create Archive" で .zip のアーカイブファイルを作成

- "Package IP and Create Arcive" は "Package IP"をドロップダウンで選択

- "General" : IP Managerを開いた際の表示を設定

- ③ IP Manager にパッケージ化したIPを追加

- "IP Manager"のアイコンをクリックし、IP Catalog のウィンドウを開く

- "+Add"で、自分で作ったIPフォルダしたの .zip を選択

- Addした後は

<Efinityインストールフォルダ>/2024.1/ipm/user_ipにIPが追加

Titaniumのコンパイル時間を短縮

Ti180, Ti375など大型のFPGAでコンパイル時間を約20%改善されました。

Ti375のサンプルデザインを使い、 コンパイル時間を計測しました。

サンプルデザインはリソース使用率は約6%、RISC-Vプロセッサ(hardend)あり、となります。

この条件で計測して、2分(10%)程度短縮されていることが確認できました。

| バージョン | 時間 |

|---|---|

| Efinity 2023.2 | 23分38秒 |

| Efinity 2024.1 | 21分378秒 |

※ CPU:Corei7-1165G7 (2.8GHz)、メモリ:16GB、の環境で各1回ずつ実行

タイミング解析用のTclスクリプトを改善

- SDC/TCL インタプリタの更新

- より多くの構文とコマンドをサポート

- 旧バージョンのワークアラウンドが不要

- GUIの更新

- コピー&ペースト、複数行の編集

- 構文のハイライト

- コマンドラインモードのサポート(efx_run.pyのフローで

sta_tclshオプションの追加) - SDCコマンドのパフォーマンス向上

- get_*コマンド実行時間の短縮

- TCLトレーニングセッションの追加

新しくサポートされたコマンド

get_fanins: ファンインポートとレジスタの文字列を返す

# Given a set of register clock pins, find the clock source

set reg_pattern "o*\[*\]~FF"

set reg_cells [ get_cells ${reg_pattern} ]

foreach reg $reg_cells {

# use get_pins to look for clock pin with pattern end with "|CLK"

set pin_pattern "${reg}|CLK"

set reg_pins [ get_pins $pin_pattern ]

# Find the clock source from register clock pins

foreach clk_pin $reg_pins {

set fanins [get_fanins $clk_pin]

puts "CLK_PIN: $clk_pin $fanins"

}

}set_bus_syntax_mode: 角かっこ[]にエスケープ文字を使用するか

# Using natural mode

set_bus_syntax_mode natural

set bus_index 10

set bus_name bus[$bus_index]

# disable natural mode

set_bus_syntax_mode disabled

set bus_index 10

set bus_name bus\[$bus_index\]create_generated_clockで利用できるオプションの増加

| 追加オプション | 説明 |

|---|---|

-phase |

マスタークロックを基準とした位相シフト(degree) |

-offset |

マスタークロックに対する絶対的な時間シフト(ns) |

-edges |

マスタークロック波形のエッジに関連する生成クロックのエッジについて、最初の立ち上がり、立下り、2つ目の立ち上がりクロックエッジをしているする3つのリスト |

-edge_shift |

-edgesで定義されたエッジに対するシフトをns単位で指定 |

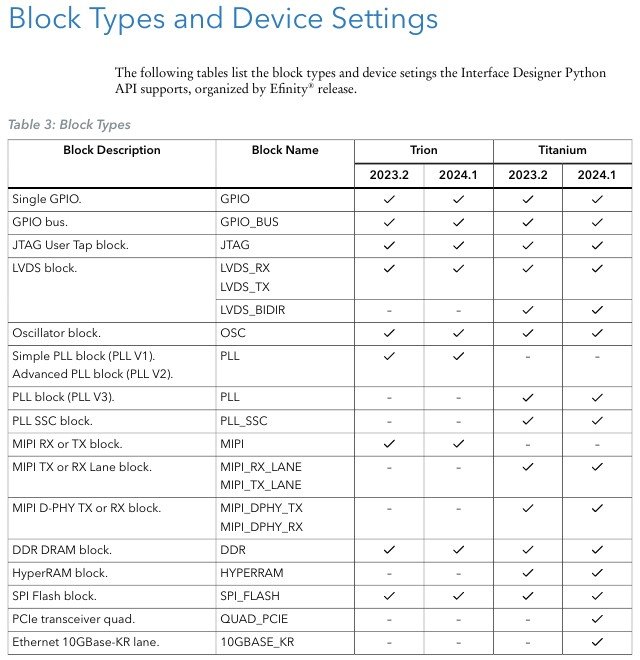

トランシーバブロックのPython APIをアップデート

Efinity Python APIで QUAD_PCIE、10GBASE_KR が追加されました。

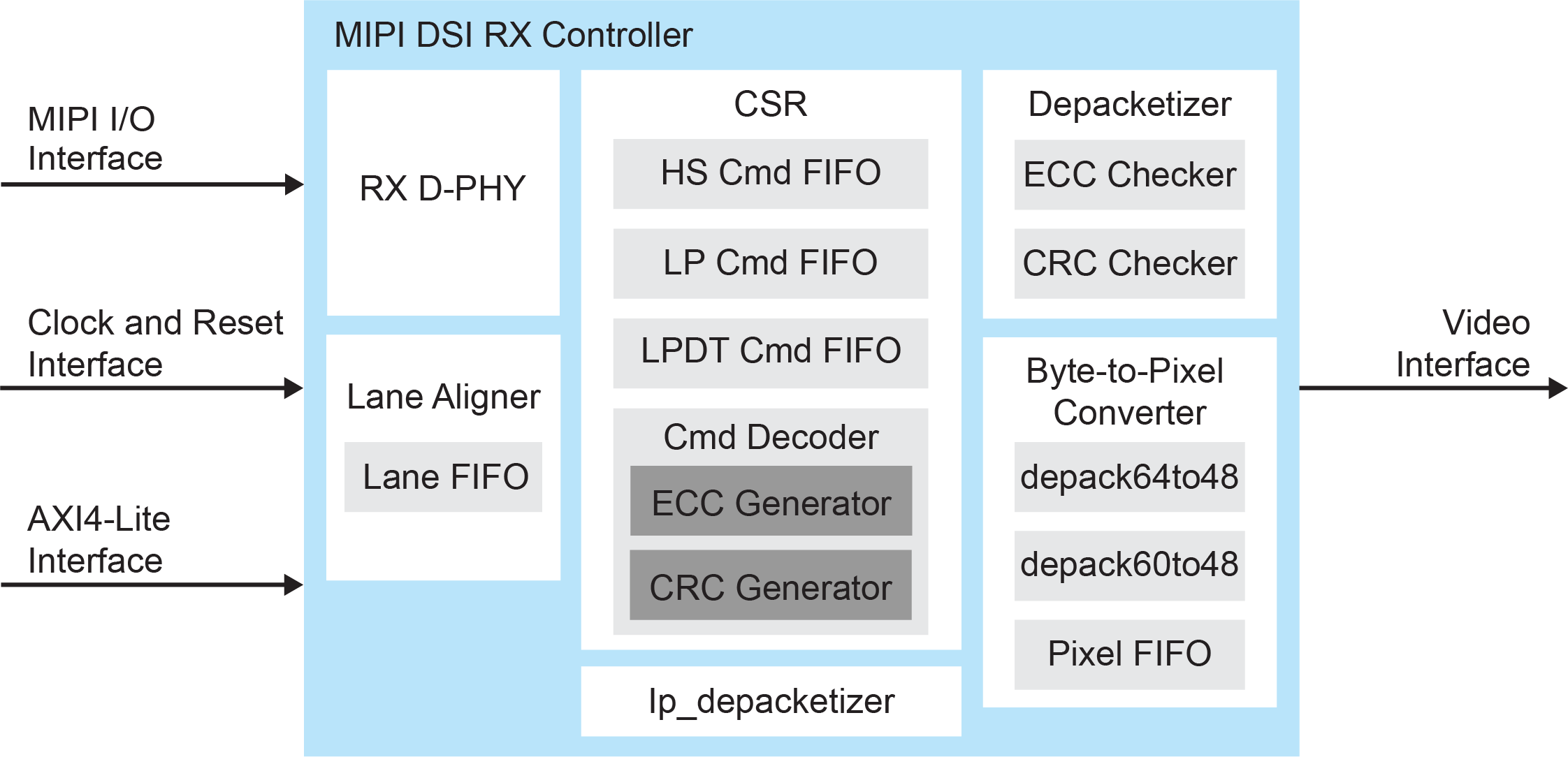

IPのアップデート

Efinity 2024.1から "MIPI DSI RX Controller Core" が追加されました。

お問い合わせ

Efinix製品に関するお問い合わせはこちらまで

https://www.explorer-inc.co.jp/contact/efinixcontact.html

デバイスのご購入やEFINIX製品へのFPGA置き換え開発についてのご相談なども受け付けています。

ご質問・ご相談などは

こちらから

お問い合わせください。