EFINIX

RISC-V Embedded Software IDE の紹介

はじめに

Efinity v2022.2.322 から新しいRISC-V開発環境として Efinity® RISC-V Embedded Software IDE (以下、RISC-V IDE)が提供されました。

ここでは、T20BGA256開発キットを使い、新しいRISC-V IDEを動かしてみたいと思います。

RISC-V IDEについて

AshlingのRiscFree IDEを搭載したEclipseベースの統合開発環境になります。従来のRISC-V SDKに比べ、プロジェクトのインポートが分かりやすくなり、ワークスペースも柔軟に設定できるようになりました。

インストール

Efinixの公式HPよりEfinity RISC-V Embedded Software IDEをダウンロードして、インストールします。

ダウンロードできない場合は、Efinix社の会員登録をしてライセンスを入手するようにしてください。

2023年4月よりライセンスがフリーになりました。

Sapphire SoCの書き込み

Sapphireとは、TrionやTitaniumのFPGA用に最適化されたソフトコアのRISC-V SoCになります。

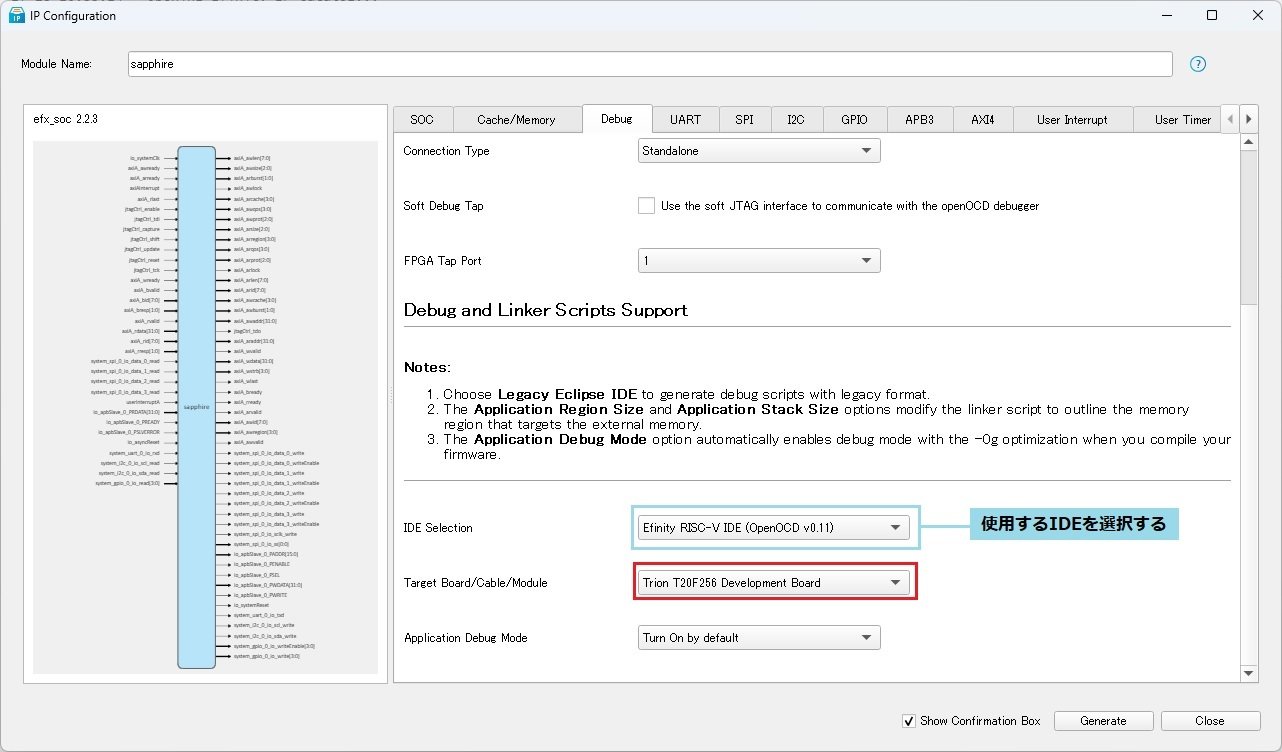

IPマネージャで様々なペリフェラルを選択しSoCを構成できます。

- Efinityを起動してプロジェクトを読み込む

- IPマネージャーでSapphire SoCの設定

- フローを実行してビットストリームを作成

- 開発キットにビットストリームを書き込み

プロジェクトのインポート

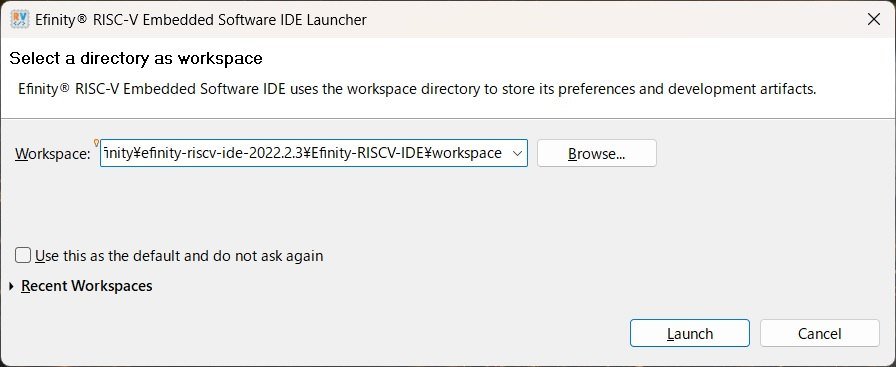

従来のRISC-V SDKではサンプルプロジェクトをワークスペースにしていましたが、新しいRSIC-V IDEでは、起動時に指定したワークスペースを使うようになりました。

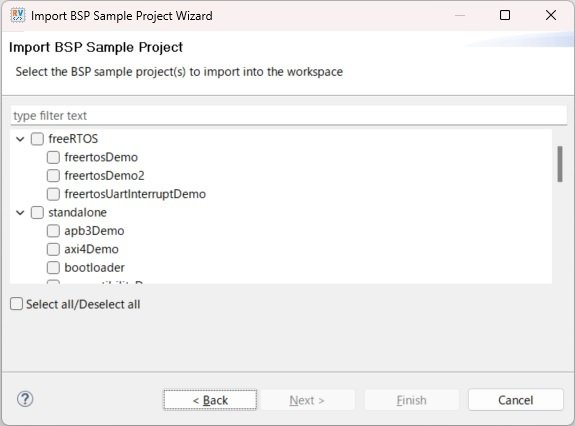

また、選択したサンプルプロジェクトをインポートできるようになりました。

- 最初にワークスペースを指定して RISC-V IDE 起動

- インポートにSapphire SoCと一緒に生成されたbspを指定

- サンプルアプリを選択してインポート

デバッグ

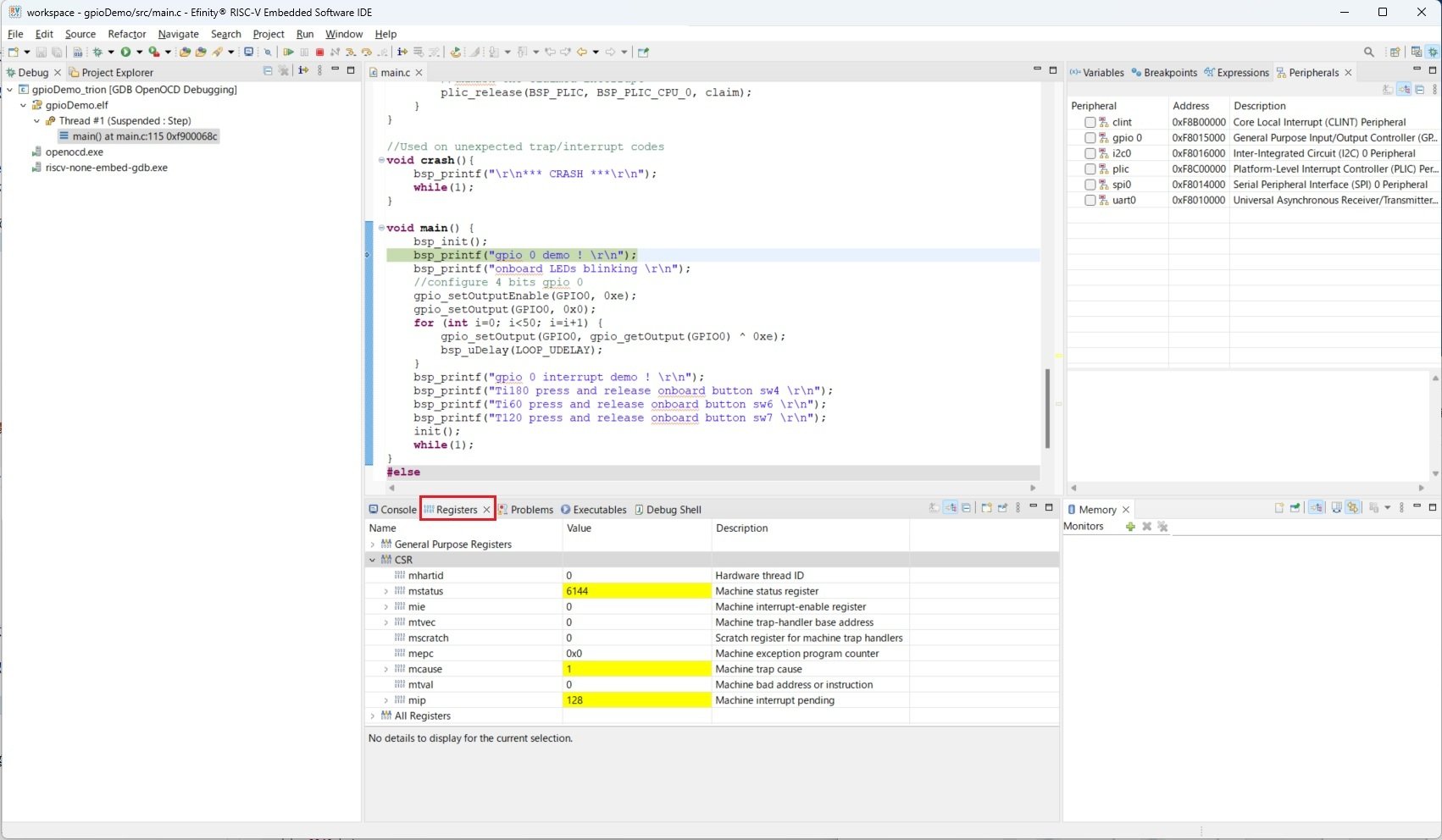

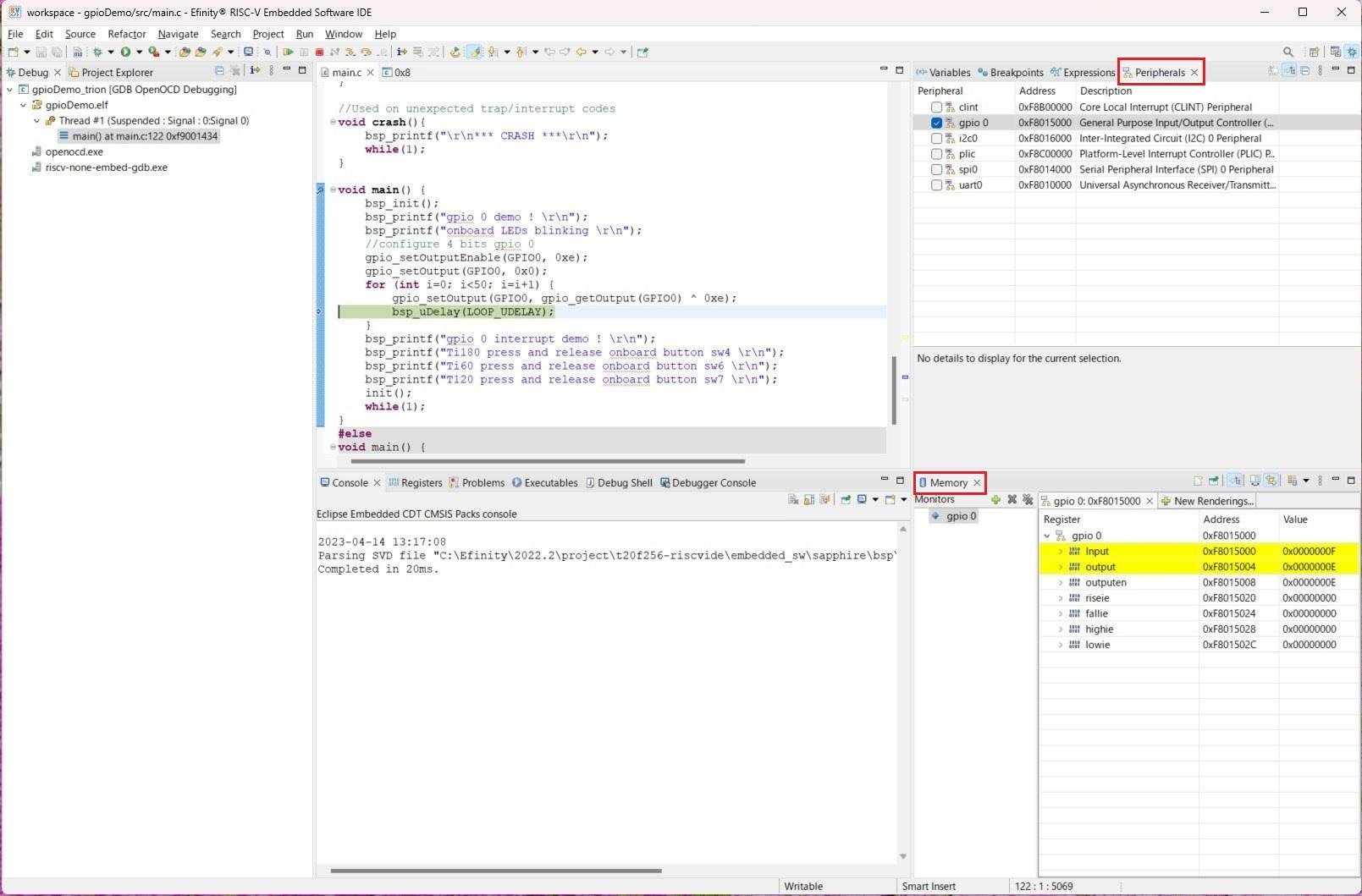

デバッグの手順は従来と同様ですが、新しいIDEでは、CSRレジスタビューとペリフェラルレジスタビューが使えるようになりました。

値が変わるとハイライトされ、レジスタの内容を確認・変更しやすくなりました。

- サンプルアプリをコンパイル

- デバッガの起動("xxxx_trion.launch"のTrion開発キット用のデバッグスクリプトを利用)

- デバッグを行う

CSRレジスタビュー

ペリフェラルレジスタビュー

お問い合わせ

Efinix製品に関するお問い合わせや技術的なサポートはこちらまで

https://www.explorer-inc.co.jp/contact/efinixcontact.html

デバイスご購入や開発についてのご相談なども受け付けています。

ご質問・ご相談などは

こちらから

お問い合わせください。