Product / Service

製品・サービス

MIPIインターフェース設計

技術概要

FPGAを用いたMIPIインタフェースの開発の課題

・ 高速信号の管理: MIPIインタフェースは一般的に高速なデータ伝送を行います。高いビットレートや高周波数信号の取り扱いには、適切

なクロック管理、信号整形、インピーダンスマッチング、クロストークの管理などが必要です。

・ クロック同期: MIPIインタフェースでは、データ転送に対してクロック信号が必要な場合があります。FPGA内でのクロック同期の方法

を考慮し、データの正確な同期を確保する必要があります。

・ 電源と信号のノイズ: FPGAボード上での電源ノイズや信号のノイズがMIPIインタフェースの動作に影響を及ぼす可能性があります。適

切な電源フィルタリング、信号経路の最適化、グランドプレーンの設計などを検討する必要があります。

・ パフォーマンスとリソース: MIPIインタフェースの実装は高いパフォーマンスを要求されることがあります。FPGAのリソースやクロッ

ク周波数などを最適に使って高い性能を達成するための最適化が必要です。

特長/性能

MIPIの開発事例

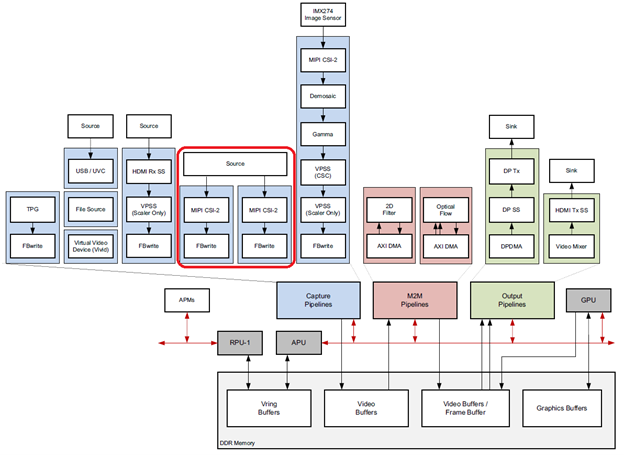

・ 4台のカメラからGMSLでデータを受信しZynqMPSoCへMIPIでデータを渡し、Displayport へ出力。

Zynq® UltraScale+™ MPSoC base targeted reference design (TRD)を使用し、下図に示すようにTRDにMIPI CSI-2 RX を2ch分追加。

⇒ご使用予定のFPGAへの転用が可能です。

構成図

MIPIの開発事例

- 4台のカメラからGMSLでデータを受信しZynqMPSoCへMIPIでデータを渡し、Displayport へ出力。

Zynq® UltraScale+™ MPSoC base targeted reference design (TRD)を使用し、下図に示すようにTRDにMIPI CSI-2 RX を2ch分追加。

⇒ご使用予定のFPGAへの転用が可能です。

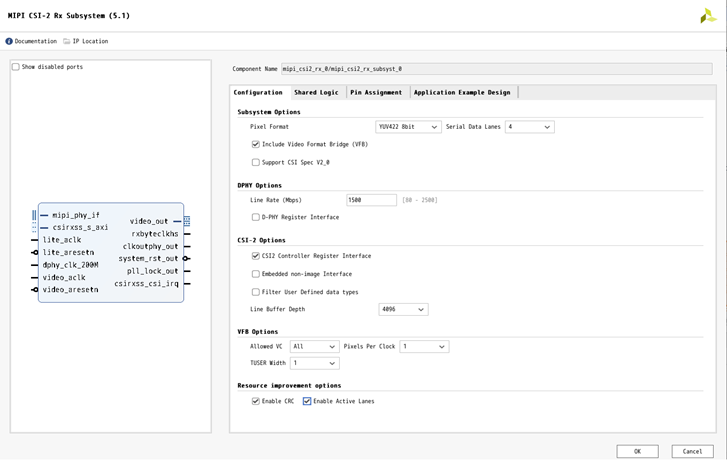

- 開発時におけるMIPIのIP設定を記載します。

Pixel Format :YUV422 8bit

Serial Data Lanes:4

Line Rate(Mbps) :1500

・基板設計時より、MIPIのIOピンに問題無いか事前にコンパイルして確認しております。

またご相談に応じてSI解析で伝送路解析を基板製造前に行い伝送路の品質を確保するように致します。

MIPIインタフェースの開発は当社にお任せください

画像システムの開発に必要な技術は多岐にわたるため、全ての分野を自社でカバーできないケースも考えられます。

- FPGA論理設計

- ホストプロセッサに搭載されるSoCのファーム開発/デバイスドライバ開発

- 評価環境構築

- 数百Mbps以上の速度が要求される基板設計・基板製造・部品調達・基板評価(試作・量産)

- 他社との差別化機能の実装

このようなお悩みに対して、弊社のデザインサービスでは、下記の通り、FPGAにまつわる知見や経験など、数十年に渡って蓄積したノウハウをバックグラウンドにした、映像システム開発のデザインサービスをご提案することが可能です。

映像システム開発に関連する課題をお抱えの場合は、弊社デザインサービスを活用いただくことで、

少しでもそれらの負荷低減を図っていただけますと幸いです。まずは下記フォームよりお気軽にお問い合わせください。

関連ソリューション

- ハードウェア設計

FPGA RTL設計サービス、Verilog-HDL/VHDL - ソフトウェア設計

ドライバ・ファームウェア開発、OSポーティング・サポート - 試作・量産ボード設計

回路図設計・レイアウト設計・基板製造・部品調達・筐体設計・部品実装まで全ての工程に対応

1台の試作から、量産ボード設計/製造までカバー