efinity-update

Efinity2023.2がリリースされました

はじめに

「Efinity統合開発ソフトウェア」は、Efinix社が提供するFPGA開発ツールで無償利用できます。 v2023.2がリリースされたので、こちらの新しい内容について見ていきたいと思います。

v2023.2のリリース内容

- Ti375C529のパッケージに対応

- 配置配線の実行時間が短縮

- PCメモリ要件が50%削減

- 論理合成オプションをアップデート

- タイミングとSDCのサポート

- SDCコマンドのテンプレートを改善

- ポイントツーポイントの combinational path delay のサポートを追加

get_fanoutsのコマンドサポート

- Efinity Programmer

- 新しくなった"SPI Active using JTAG Bridge"

- ビルド済みのフラッシュローダ

- IP Manager

- Sapphire High-Perfomance RISC-V IPコアのフローを合理化

Ti375C529のパッケージに対応

Efinity2023.2から、Ti375C529に対応しました。

従来はTi180まででは難しかった中規模のFPGA置き換えも採用できます。

また、Ti375C529で hardend RISC-V がご利用いただけるようになりました。

他社のFPGAと比較してパッケージが小さなっており、低消費電力になります。

さらに、短納期・安定供給で2037年までの長期供給をサポートしていています。

Xilinx社のKintex-7、Intel社のArriaVとの比較を表にまとめました。

| デバイス | Ti375C529 | Kintex-7 XC7K355T | ArriaV 5ASTD3 |

|---|---|---|---|

| ロジックエレメント(LE) | 370,137 | 356,160 | 350,000 |

| エンベデッドメモリー(Kb) | 27,530 | 25,740 | 19,304 |

| DSP | 1,344 | 1,440 | 809 |

| PLL | 12 | 6 (CMT) | 14 |

| ハード化されたCPU | Quad-core RISC-V | × | Dual-Core Arm Coretex-A9 |

| メモリコントローラ | LPDDR4 | DDR3 | DDR3 |

| 高速トランシーバ | × | Max 24 (12.5Gpbs) | Max 46 (10.3125Gbps) |

| PCI Gen2 | × | 〇 | 〇 |

| パッケージ | C529 (19x19mm) | FFG901 (31x31mm) | F896 (31x31mm) |

配置配線の実行時間が短縮

Titanium FPGAで配線の時間が3倍高速になり、全体的な配置配線の実行時間は50%短縮されました。

Efinity2023.2とEfinity2023.1でコンパイル時間を比較してみます。

サンプルプロジェクトは"Edge Vision SoC"のTi180J484_coral_hdmi(リソース使用率25%)を利用して、測定しました。

今回の例では、配置配線が5%程度短縮されているのが確認できます。

| Version | Efinity2023.2 | Efinity2023.1 |

|---|---|---|

| 合計時間 | 28分25秒 | 28分45秒 |

| 論理合成 | 7分8秒 | 6分00秒 |

| 配置 | 14分55秒 | 16分02秒 |

| 配線 | 6分00秒 | 6分30秒 |

| ビットストリーム生成 | 15秒 | 13秒 |

※ PCのスペック、CPU:Core i7-1165G7(2.8GHz)、メモリ:16GB

※ Efinity2023.2ではプロジェクトのIPをアップグレード

PCメモリ要件が50%削減

Efinityを利用するPCメモリ要件が50%削減されま、ハードウェアのメモリ要件は次の表のようなりました。

従来のTrion/TitaniumでのPC要求スペックが下がり開発しやすくなっています。

| Version | Efinity2023.2 | Efinity2023.1 |

|---|---|---|

| T4, T8, T13, T20, T35 | 8GB | 16GB |

| T55, T85, T120 | 16GB | 32GB |

| Ti36, Ti60 | 8GB | 16GB |

| Ti90, Ti120, Ti180 | 16GB | 32GB |

| Ti375 | 32GB | - |

論理合成オプションのアップデート

論理合成オプションとして以下が追加されました。

--use-logic-for-small-mem- LEで実装される小さなRAMブロックの制限を設定

--use-logic-for-small-rom- LEで実装される小さなROMブロックの制限を設定

--mult-auto-pipeline- ワイドな乗算器に対して自動パイプライン化を実行し、レイテンシの増加を代償に性能を向上させる

- 部分乗算と部分和の出力にパイプラインレジスタを挿入し、DSP48にPレジスタ、Wレジスタとしてパック

- 乗算器の入力と出力に追加のレジスタを挿入し、前のレジスタ挿入によって引き起こされるレイテンシの問題を調整

タイミングとSDCのサポート

SDCコマンドのテンプレートを改善

SDCコマンドのテンプレートについて delay の手動計算が不要になりました。

Interface Designerで"Generate Efinity Constraint Files"を実行すると、SDCのテンプレートファイルやタイミングレポートが生成されます。

Efinity2023.1は、GPIOのクロックdelayを設定する場合、タイミングレポート(<project>.pt_timing.rpt)を確認してSDCファイルに以下のようなdelayの設定を入れる必要がありました。

set_clock_latency -source -setup <max calculation> <clock ports>

set_clock_latency -source -hold <min calculation> <clock ports>

Efinity2023.2では、テンプレートファイル(<project>.pt.sdc)を生成時に"Clock Latency Constraints"の項目が追加されるようになりました。

タイミングレポート(<project>.pt_timing.rpt)に表示されるGPIOクロックバッファのdelay

Non-registered HSIO GPIO Configuration:

========================================

+---------------+----------+-------------+----------+----------+

| Instance Name | Pin Name | Parameter | Max (ns) | Min (ns) |

+---------------+----------+-------------+----------+----------+

| clk | clk | GPIO_CLK_IN | 0.828 | 0.552 |

| i | i | GPIO_IN | 0.828 | 0.552 |

| o | o | GPIO_OUT | 2.205 | 1.470 |

+---------------+----------+-------------+----------+----------+

SDCのテンプレートファイル

# Clock Latency Constraints

############################

# set_clock_latency -source -setup <board_max + 0.828> [get_ports {clk}]

# set_clock_latency -source -hold <board_min + 0.552> [get_ports {clk}]

ポイントツーポイントの combinational path delay のサポートを追加

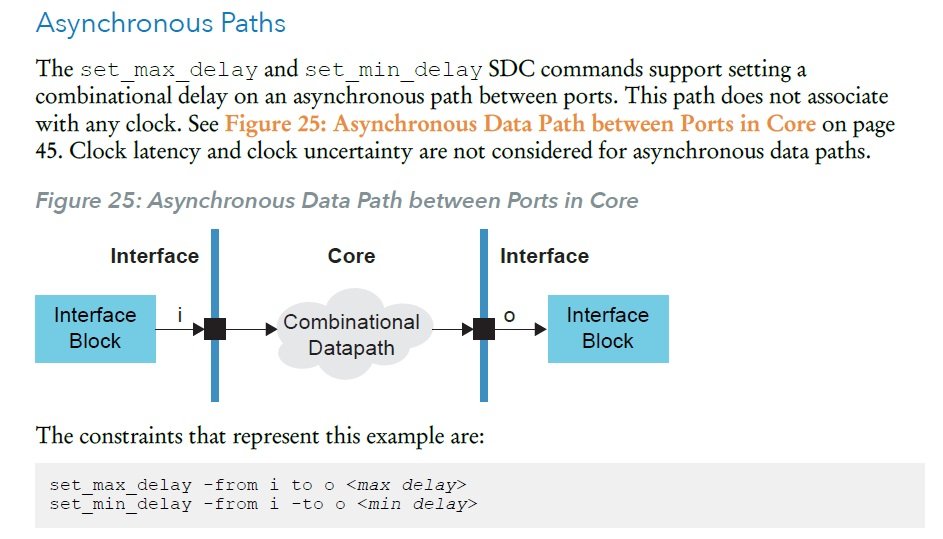

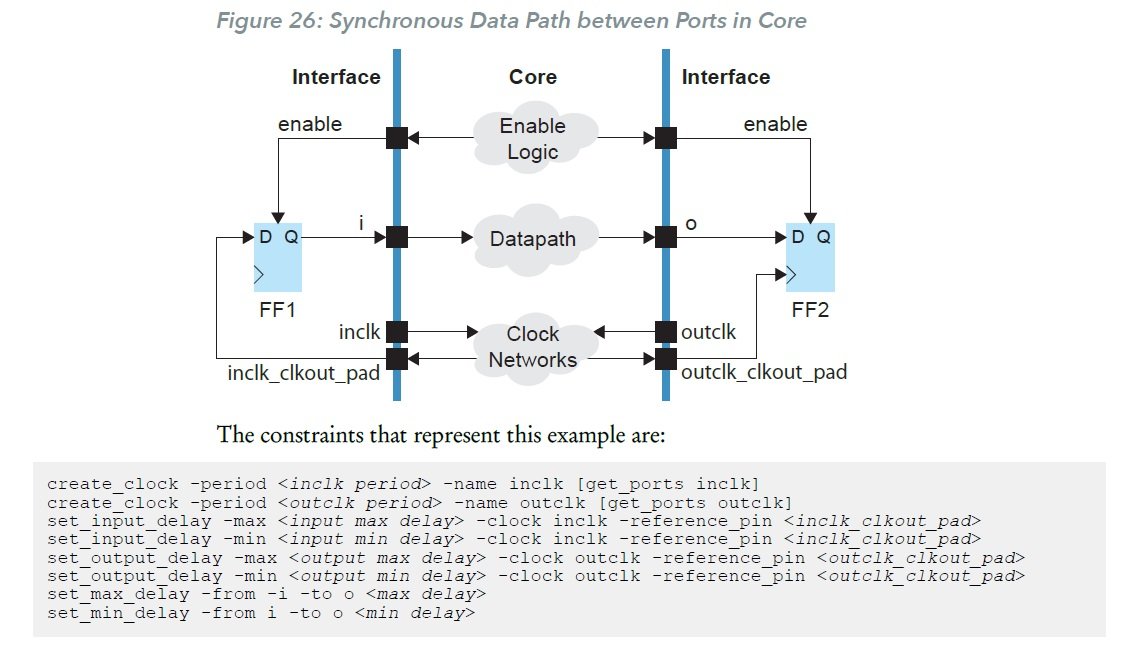

Efinityのタイミング設定について、Efinity Timing Closure User Guide v5.0 で、min/Max Delayに3つのパスの説明が追加されました。

- Efinity Timing Closure User Guide v5.0

- Timing Exceptions

- Understanding Min and Max Delays

- Asynchronous Paths

- Synchronous Paths

- Mixed Asynchronous and Synchronous Paths

- Understanding Min and Max Delays

- Timing Exceptions

ドキュメントで追加された説明の例

get_fanoutsのコマンドサポート

Efinity2023.2からget_fanoutsのコマンドがサポートされました。

このコマンドは指定した名前のファンアウトであるポートまたはレジスタを返します。

オプションについてくわしくは Efinity Timing Closure User Guide v5.0 をご確認ください。

get_fanouts [-no_logic] -through <names> <start point>

Efinity Programmer

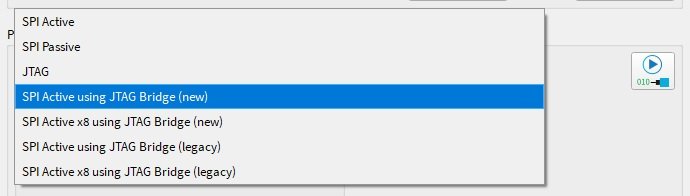

新しくなった"SPI Active using JTAG Bridge"

"SPI Active using JTAG Bridge"が新しくなり従来のものより高速化しました。

Efinty2023.2のフラッシュ書き込みでは、"SPI Active using JTAG Bridge"は次のように、LegacyとNewの2つになりました。

- SPI Active using JTAG Bridge (New)

- v2023.1以前のものと同様の動作

- T20BGA256評価ボードのサンプル書き込みは14秒

- SPI Active using JTAG Bridge (Legacy)

- v2023.2以降で利用できLegacyより高速化

- あらかじめビルドされたフラッシュローダ(.bit)が用意

- T20BGA256評価ボードのサンプル書き込みは11秒

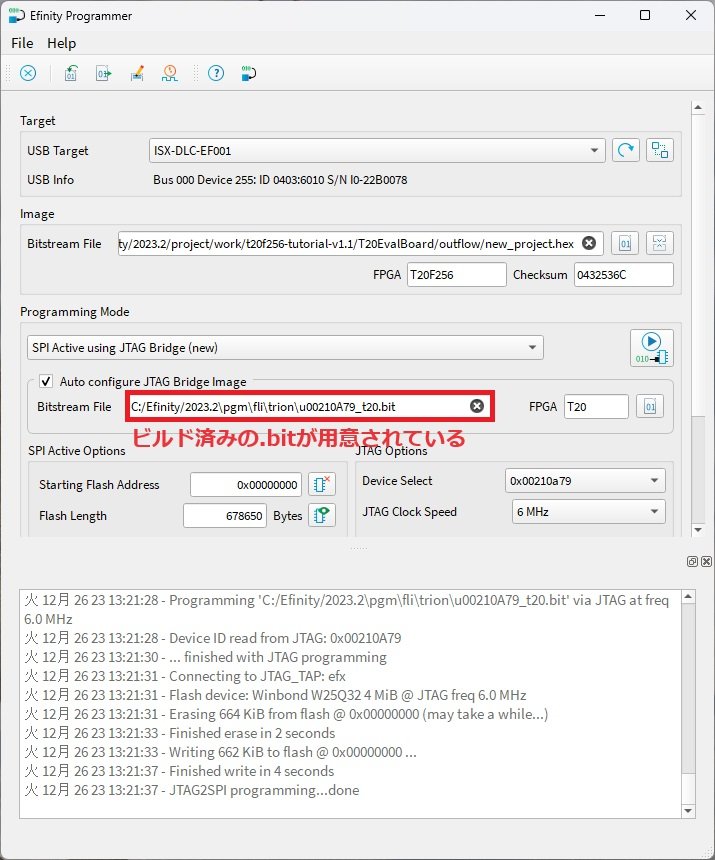

ビルド済みのフラッシュローダ

"SPI Active using JTAG Bridge"で利用するビルド済みの.bitが用意されていて、自分で"JTAG SPI Flash Loader"のIPを入れたプロジェクトを作る必要がありません。

<Efinityインストールディレクトリ>/pgm/fli/<family>

IP Manager

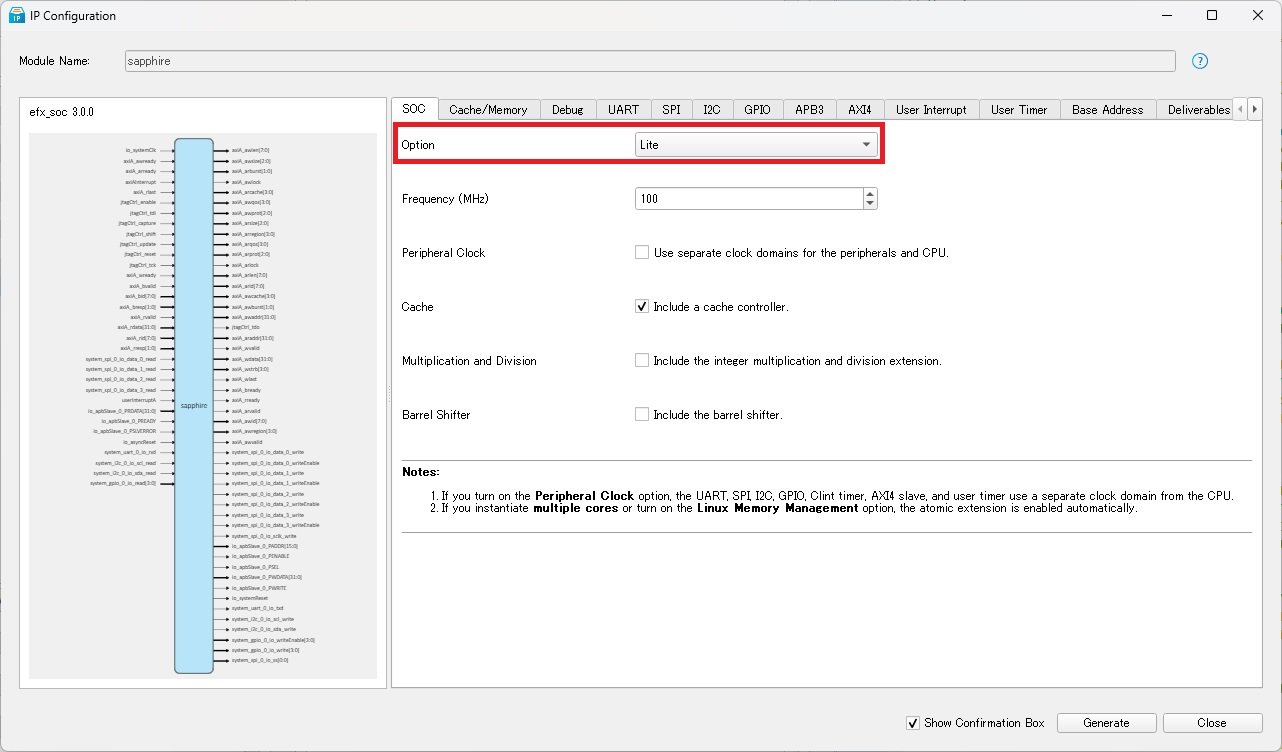

Sapphire High-Perfomance RISC-V IPコアのフローを合理化

Sapphire SoCは2つのオプションがあり、異なるニーズや用途に対応できるようになりました。

Sapphore SoCのカスタマイズはIPウィザードで行います。

パラメータはタブで表示され、クリックすることで簡単に確認できます。

選択したオプション(Standard / Lite)により、SoCタブとキャッシュ/メモリタブが変わってきます。

- Standard

- 最高性能を達成するため、より多くのリソースを使用します。

- Lite

- 最小面積にするため、SoCの性能を制限し高度な機能は利用できません

お問い合わせ

Efinix製品に関するお問い合わせや技術的なサポートはこちらまで

https://www.explorer-inc.co.jp/contact/efinixcontact.html

デバイスご購入や開発についてのご相談なども受け付けています。

ご質問・ご相談などは

こちらから

お問い合わせください。